CHƯƠNG TRÌNH TUYỂN DỤNG THỰC TẬP SINH 2023

Category : Tuyển dụng

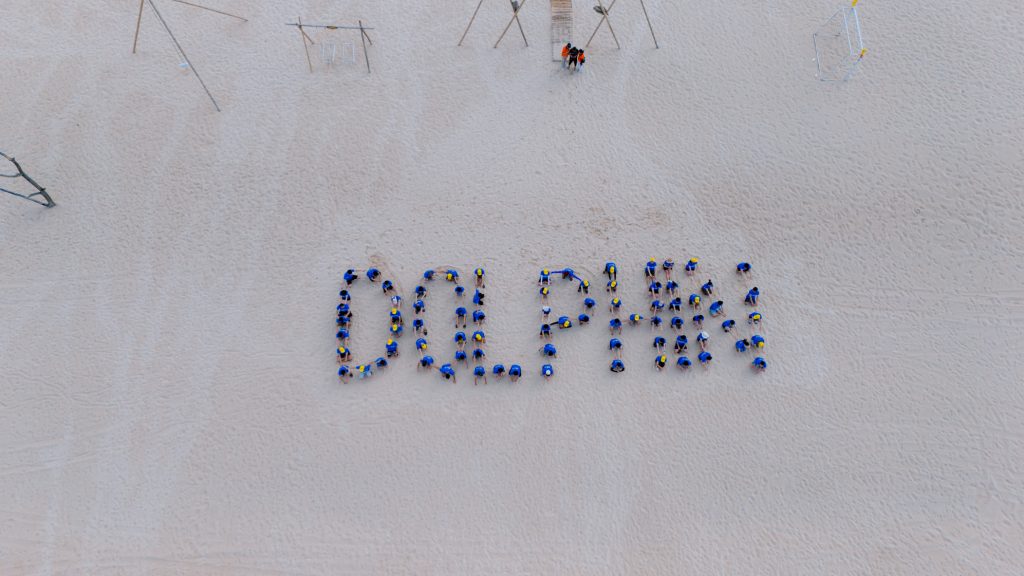

Dolphin Technology Vietnam Center là 1 trong số các công ty Thiết kế Vi mạch hàng đầu tại Việt Nam. Với sứ mệnh “To be Silicon IP Experts”, chúng tôi luôn đề cao sự đam mê, học hỏi và không ngại khó. Chúng tôi luôn nỗ lực mang đến 1 môi trường làm việc sôi nổi, trẻ trung, thoải mái cũng như những chế độ ưu đãi tuyệt vời dành cho tất cả Dolphin-er.

Hiện nay, Dolphin Technology Vietnam Center đang tuyển dụng Thực tập sinh các vị trí Physical Design: Thiết kế Memory, StandardCells Layout.

Quyền lợi của thực tập sinh

- Được đào tạo về các ngôn ngữ lập trình phần cứng và phần mềm như: Verilog, System Verilog. C, C++,…

- Được tham gia vào quá trình phân tích, thiết kế, đưa ra các giải pháp, ý tưởng cho sản phẩm thực tế mà công ty đang phát triển (bộ nhớ SRAM, flow, Semiconductor IP,…)

- Được đào tạo, trải nghiệm và làm việc trực tiếp để củng cố kiến thức, tích lũy kinh nghiệm liên quan đến timing, power

- Được làm việc với các dự án thực tế theo những công nghệ thiết kế vi mạch hàng đầu hiện nay cùng các nhân sự giàu kinh nghiệm, hướng dẫn nhiệt tình, bài bản

- Thời gian làm việc linh hoạt, ưu tiên tối đa sắp xếp cân đối giữa việc học tại trường và thực tập tại công ty

- Được hưởng trợ cấp thực tập từ 4,000,000 – 8,000,000 đồng/tháng

- Tham gia du lịch, nghỉ mát hàng năm, các hoạt động team building, thể thao, sự kiện của công ty.

=> Cơ hội trở thành nhân viên chính thức sau khi hết thời gian thực tập hoặc chuyển sang làm việc theo diện cộng tác viên với nhiều quyền lợi hấp dẫn.

Đối tượng tham gia chương trình thực tập sinh

- Sinh viên các năm thứ 4, thứ 5 các ngành Điện tử, Điện tử viễn thông, Công nghệ thông tin, Công nghệ máy tính

- GPA >=2.8 hoặc có khả năng lập trình thành thạo.

HỒ SƠ ỨNG TUYỂN

- CV có ảnh (bắt buộc), nêu rõ kinh nghiệm, các dự án nghiên cứu, làm việc (nếu có). Ưu tiên CV viết bằng tiếng Anh

- Bảng điểm, chứng nhận kết quả học tập. Có thể download từ trang web của nhà trường, bản có dấu xác nhận có thể nộp sau để đối chiếu theo yêu cầu của công ty

- Chứng chỉ, bằng cấp khác (nếu có)

- Chỉ nhận hồ sơ ứng tuyển qua email: jobs@dolphin-vc.com

- Tiêu đề email viết theo mẫu: Vị trí ứng tuyển_Họ và tên

- Hạn nộp hồ sơ: 31/12/2023

THÔNG TIN LIÊN HỆ

- Công ty TNHH Dolphin Technology Vietnam Center

- Tầng 2 – tòa nhà LiLama – số 124 Minh Khai – Hai Bà Trưng – Hà Nội

- ĐT: 0243.624.9784

- Email: jobs@dolphin-vc.com

- Fanpage: https://www.facebook.com/dolphin.jobs

- Linkedin : https://www.linkedin.com/company/dolphin-technology-vietnam-center

- Twitter: https://twitter.com/Dolphin_DTVC